|

ˇˇ |

|

Project Maintainer: Yu Lu |

|

|

|

|

|

|

|

|

|

|

|

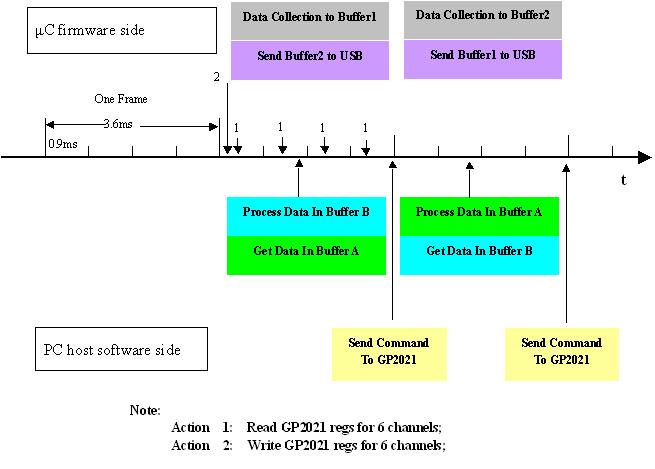

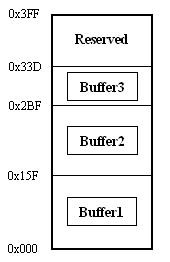

Collection 1(updated in the first 0.9MS ) : accum_status_c,meas_status_a,accum_status_a,accum_status_b;( 8 bytes) 6 channels' accumulation data; ( 6*8 bytes) | |

|

Collection 2(updated in the second 0.9MS ) : accum_status_c,meas_status_a,accum_status_a,accum_status_b;( 8 bytes) 6 channels' accumulation data; ( 6*8 bytes) |

|

|

Collection 3(updated in the third 0.9MS ) : accum_status_c,meas_status_a,accum_status_a,accum_status_b;( 8 bytes) 6 channels' accumulation data; ( 6*8 bytes) |

|

|

Collection 4(updated in the fourth 0.9MS ) : accum_status_c,meas_status_a,accum_status_a,accum_status_b;( 8 bytes) 6 channels' accumulation data; ( 6*8 bytes) |

|

|

6-channels' measurement( updated only when TIC happens) : Each channel has : CODE_SLEW,CODE_PHASE, CARRIER_CYCLE_LOW, CARRIER_DCO_PHASE, EPOCH,CODE_DCO_PHASE,CARRIER_CYCLE_HIGH,EPOCH_CHECK; ( 6*16 bytes) |

|

| Timestamps for 4 collections; ( 4 bytes) | |

| Debug info or reserved for future; ( 28 bytes) |

|

Flag: ( 1 bytes) 1: PC wants firmware to send collections ; 0: PC donot want firmare to send collections; |

|

|

Number of commands; (1 byte) Must be less than 41; |

|

Command 1: (3 bytes)

|

|

|

|

|

Command 41: (3 bytes)

|